Mahmood Rafiee

Publications

Under review

J1. Highly Doped and Optimized 5-nm GAA CNTFET with Different Perspectives

• Submitted to IEEE Transaction on Electron Device (January 2023/ Major revised)

J2. High-Efficient Accurate and Stable Approximate Subtractors for Change Detection in Bi-Temporal Images

• Submitted to The IEEE Transactions on Circuits and Systems II: Express Briefs (July 2023)

J3. Unlocking the Concept of Approximate Computing for Fault-Susceptible Applications Using High-Efficient Sum of Absolute Difference Unit

• Submitted to IEEE Transactions on Nanotechnology. (Aug 2023)

Peer-Reviewed Journals

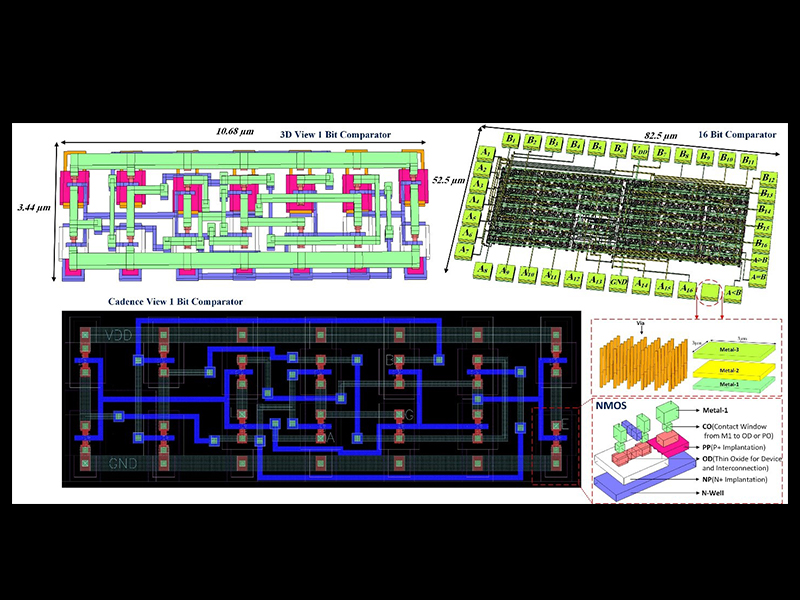

J1. Low-Power and Fast-Swing-Restoration GDI-Based Magnitude Comparator for Digital Images Processing.

Mahmood Rafiee, Dr. Nabiollah Shiri, Ayoub Sadeghi, Abdolreza Darabi, Ebrahim Abiri.

Circuits, Systems, and Signal Processing, 39, 4516–4551, 2020, http://dx.doi.org/10.1007/s00034-022-01997-6

A new 1-bit digital comparator named 14T-SR-GDI is presented with gate-diffusion-input (GDI) and single-swing-restoration (SR) techniques to attain internal gates with high driving capability.

The comparator has 14 transistors which produce full-swing outputs with low power consumption.

In the 14T-SR-GDI, boosted inner signals are used to activate the output gates which result in a high-speed circuit with effective scalability and the enhanced driving capability for multi-bit structures.

The comparator has a low power-delay-product (PDP) due to the small numbers of internal nodes and capacitances and efficient power-ground-free gates.

The 14T-SR-GDI comparator, fully SR-GDI-based AND, and OR gates, construct a new tree structure for multi-bit magnitude comparators including 2-bit, 4-bit, 8-bit, and 16-bit comparators.

The proposed 1-bit comparator is used in image processing for difference detection, and its efficiency is proved by image quality parameters.

The post-layout simulations are performed for the 1-bit to 16-bit structures under TSMC 90 nm technology.

The extracted results express a PDP with an average difference of 9.59% between the regular and post-layout modes.

Also, the proposed 16-bit comparator is embedded in a pad with a total area of 4331.25 μm2. The designed magnitude comparators are key components in digital signal processors (DSPs).

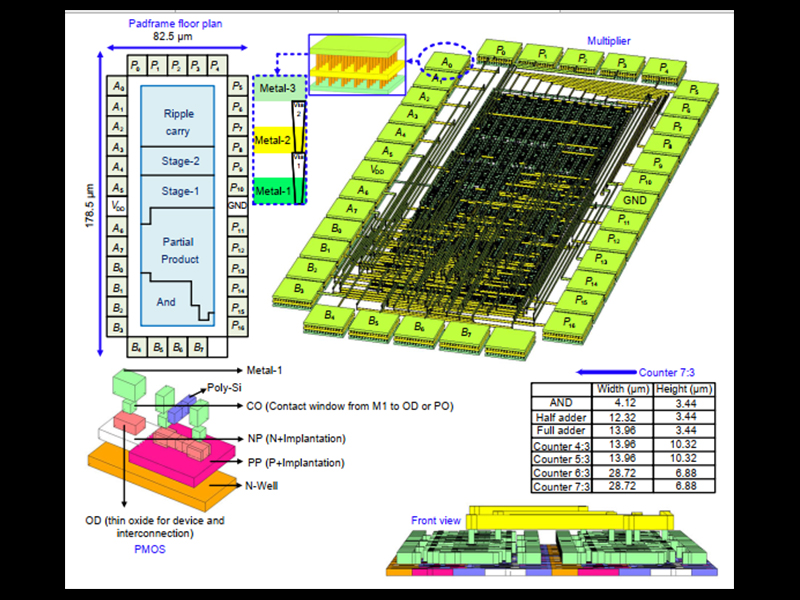

J2. An efficient counter-based Wallace-tree multiplier with a hybrid full adder core for image blending.

Ayoub Sadeghi, Dr. Nabiollah Shiri, Mahmood Rafiee, Mahsa Tahghigh

Frontiers of Information Technology & Electronic Engineering 23(6):950-965,

http://dx.doi.org/10.1631/FITEE.2100432.

We present a new counter-based Wallace-tree (CBW) 8×8 multiplier.

The multiplier's counters are implemented with a new hybrid full adder (FA) cell, which is based on the transmission gate (TG) technique.

The proposed FA, TG-based AND gate, and hybrid half adder (HA) generate M:3 (4⩽M⩽7) digital counters with the ability to save at least 50% area occupation.

Simulations by 90 nm technology prove the superiority of the proposed FA and digital counters under different conditions over the state-of-the-art designs.

By using the proposed cells, the CBW multiplier exhibits high driving capability, low power consumption, and high speed.

The CBW multiplier has a 0.0147 mm 2 die area in a pad. The post-layout extraction proves the accuracy of experimental implementation.

An image blending mechanism is proposed, in which a direct interface between MATLAB and HSPICE is used to evaluate the presented CBW multiplier in image processing applications.

The peak signal-to-noise ratio (PSNR) and structural similarity index metric (SSIM) are calculated as image quality parameters,

and the results confirm that the presented CBW multiplier can be used as an alternative to designs in the literature.

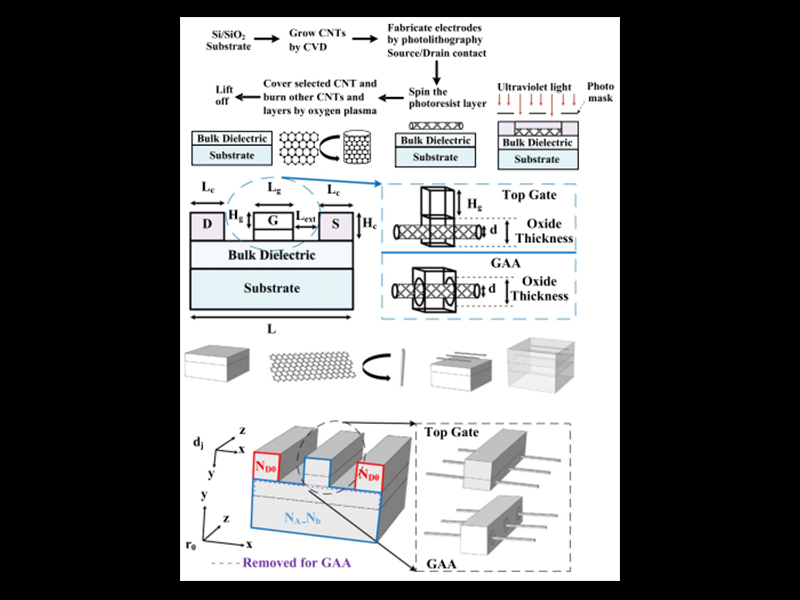

J3. Characteristics Extraction of Fully Symmetric GAA and Top-Gate CNTFETs with 6 nm Channel Length

Dr. Nabiollah Shiri, Mahmood Rafiee,Ayoub Sadeghi, Rahim Ghayour

ECS J. Solid State Sci. Technol. 11 061009,

http://dx.doi.org/10.1149/2162-8777/ac7613 .

High-compatible applications for top-gate and gate-all-around (GAA) carbon nanotube field-effect transistors (CNTFETs) are presented.

The geometrical specifications of these CNTFETs are evaluated and their effects on the characteristics are highlighted.

The channel length is considered 6 nm, while the drain, source, and spacer are symmetric with channel length.

The evaluations are performed by the COMSOL Multiphysics, and the Shockley-Read-Hall (SRH) recombination model is used to analyze doping, electron, and hole distributions.

The drain and source wells are considered with donor doping of ND0=1×1021 cm-3 and acceptor doping of NA=1×1019 cm-3, then,

the current-voltage (I-V) characteristics are extracted. Also, the CNTs with 1.12 nm are placed accurately through the channel, and the terminals are constructed with graphene.

The I-V curves show that the threshold voltage for the top-gate and GAA are 0.23 and 0.21 V, respectively. In addition, the short channel effect (SCE) is reduced which is confirmed by a subthreshold swing (SS) of 62 mV/dec for the top-gate and 58 mV/dec for the GAA. Moreover,

drain-induced barrier lowering (DIBL) and ION/IOFF ratio parameters are studied to investigate scaled-down devices. The discussed structures are compared by the figure of merit (FoM) of ΔVDIBLSS/(ION/IOFF), which shows more desirable and better channel control.

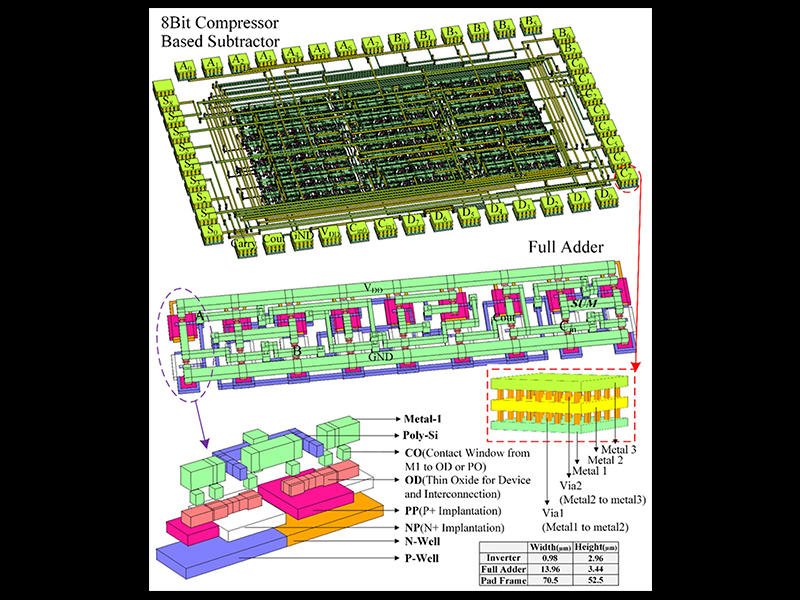

J4. Tolerant and low power subtractor with 4:2 compressor and a new TG‐PTL‐float full adder cell

Ayoub Sadeghi, Dr. Nabiollah Shiri, Mahmood Rafiee, Rahim Ghayour

IET Circuits, Devices and Systems 16(1), http://dx.doi.org/10.1049/cds2.12117 .

A new 1‐bit full adder (FA) cell illustrating low‐power, high‐speed, and a small area is presented by a combination of transmission gate (TG), pass transistor logic (PTL), and float techniques. Using the proposed cell, a 4:2 compressor is implemented and its performance is investigated under diverse circumstances of voltage, temperature, and driving.

The process and corners are evaluated through the process‐voltage‐temperature (PVT) variations and the Monte Carlo method (MCM), respectively.

The accuracy and reliability of the proposed 4:2 compressor are confirmed carefully.

Utilising the proposed FA and the compressor, an efficient 8‐bit subtractor is implemented for bioimage processing, in particular for difference detection of images.

A new mechanism is presented to improve the detection performance of digital signal processors (DSPs) by the addition and subtraction of two images for their difference.

The quality of the resulted image confirms the efficiency of the proposed circuits and the method.

The high performance of the circuits makes them a promising candidate for the next generation of integrated circuits (ICs) applicable to medical image processing.

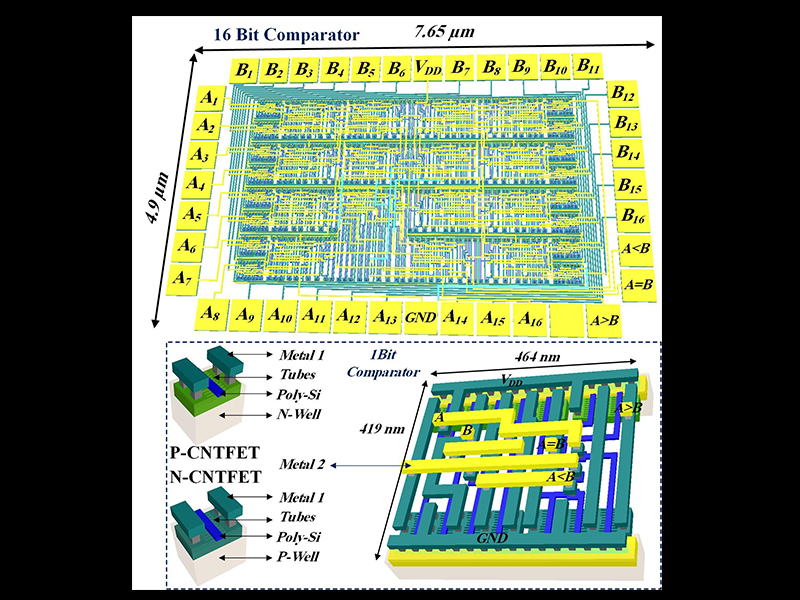

J5. SR‐GDI CNTFET‐based magnitude comparator for new generation of programmable integrated circuits

Dr. Nabiollah Shiri, Ayoub Sadeghi,Mahmood Rafiee, Maryam Bigonah

Int J Circ Theor Appl. 2022; 50( 5): 1511- 1536, http://dx.doi.org/10.1002/cta.3251 .

The performance of the programmable integrated circuits (ICs) like digital signal processors (DSPs), central processing units (CPUs),

and microcontrollers is highly dependent on the magnitude comparators.

This article presents a new reliable and efficient 1-bit comparator based on carbon nanotube field-effect transistors (CNTFETs) technology.

The gate diffusion input (GDI) technique is used to reduce the number of transistors.

Also, single swing restoration (SR) transistors and transmission gate (TG) techniques are combined to attain full-swing outputs with high driving capability.

The low internal capacitances and the fewer number of internal nodes of the proposed comparator make it low-power both in single-bit and multibit (2-bit, 4-bit, 8-bit, and 16-bit) implementations.

Variations analyses of the circuit and technology parameters are performed that show the cell efficiency.

From the layout results, the 1-bit and 16-bit comparators occupy 0.1944 μm2 and 37.485 μm2 as the total die area, respectively.

The proposed circuit is implemented in image processing in which the best performance compared with state-of-the-art designs regarding hardware complexity, circuitry performance, and image quality assessments are confirmed, by at least 50% improvements of different critical parameters.

The resulted figure of merits nominates the cell for future ICs.

J6. An efficient multiplier by pass transistor logic partial product and a modified hybrid full adder for image processing applications

Mahmood Rafiee, Farshad Pesaran, Ayoub Sadeghi, Dr. Nabiollah Shiri.

Microelectronics Journal, 2021,https://doi.org/10.1016/j.mejo.2021.105287.

Different digital multipliers have resulted from various algorithms and hardware designs.

This article presents a high-performance multiplier by a novel AND gate and a modified hybrid full adder (FA) cell.

The AND is designed by using the pass transistor logic (PTL) technique and a speed-up transistor, while the FA is based on the transmission gate (TG).

Low-power, high-speed, low power-delay-product (PDP), and high competency of both circuits for using in sophisticated structures like multipliers are confirmed by mathematical relations.

The proposed 4-bit array multiplier circuit along with the pad has a 2.87 mm² total area and is investigated under different circumstances including VDD, frequency, load capacitances, and process-voltage-temperature (PVT) variations using Monte Carlo method (MCM) by HSPICE tool and 90 nm technology.

The efficiency of the multiplier in image processing applications is proved with average improvements of 12.61% and 32.045% for peak signal-to-noise ratio (PSNR) and PDP compared to state-of-the-art designs, respectively.

The overall results of the multiplier approve its capability for digital signal processors (DSPs).

J7. High-Performance 1-Bit Full Adder with Excellent Driving Capability for Multistage Structures.

Mahmood Rafiee, Dr. Nabiollah Shiri,Ayoub Sadeghi.

IEEE Embedded Systems Letters, August 2021, doi: 10.1109/LES.2021.3108474.

In this brief, a low-power 1-bit full adder (FA) cell is proposed based on the transmission gate (TG) to attain a special module for generating full swing Carry output.

The cell benefits from the high driving capability for both Sum and Carry outputs when embedding in multistage structures like ripple carry adders (RCAs), compressors, and multipliers.

The proposed TG-based FA has a total die area of 60.02 μm2, while the average power, delay, and power-delay-product (PDP) are 10.829 μW, 3.1954 ns, and 34.603 fJ, respectively.

The results introduce the FA cell as an efficient gate for integrated circuits (ICs).

J8. An approximate CNTFET 4:2 compressor based on gate diffusion input and dynamic threshold.

Mahmood Rafiee, Yaqhoub Sadeghi,

Dr. Nabiollah Shiri,

Ayoub Sadeghi.

Electronic Letter, 57: 650-652, 2021, https://doi.org/10.1049/ell2.12221.

In this paper, a new 4:2 approximate compressor is presented by the gate diffusion input (GDI) technique.

Although GDI cells suffer from threshold voltage drop, the dynamic threshold (DT) approach and carbon nanotube field-effect transistors (CNTFETs) are merged to overcome the mentioned problem.

The proposed cell has full-swing outputs, while its error and power delay product (PDP) are at low rates.

Low voltage multipliers that are used in image processing can benefit from the proposed compressor.

J9. Ultra-Low-Power and High-Speed 4:2 Compressor with a New Full Adder Cell for Bioelectronics Applications.

Ayoub Sadeghi, Dr. Nabiollah Shiri, Mahmood Rafiee.

Circuits, Systems, and Signal Processing, 39, 6247–6275, 2020, https://doi.org/10.1007/s00034-020-01459-x.

Size reduction in complementary metal–oxide–semiconductor integrated circuits (ICs) is a challenge.

Carbon nanotube field effect transistor (CNTFET) technology with advantages such as low power, high mobility, and ballistic transmissions is an alternative. Based on the standard 32 nm CNTFET technology, a new 23-transistor full adder cell is proposed with combining advantages of gate diffusion input and transmission gate techniques, which are low power and full swing.

Owing to small number of transistors and internal nodes, the delay time and activity factor decreased to 13.5τ.

Simulations of critical parameters variations like VDD, temperature, and fan-out expose better performance of the proposed cell.

Investigating the process voltage temperature with Monte Carlo simulation verified better stability, immunity, and tolerability of the cell in comparison with well-known full adder cells.

Suggested full adder cell was implemented in 4:2 compressor with 9.0298 fJ of power delay product and minimum area occupation among the references.

Based on real chip measurements, total die area occupation for proposed full adder and compressor is 0.505 µm2 and 1.092 µm2, respectively.

Proposed circuits were applied to an 8-bit subtractor for orthopantomogram image processing to detect tooth core build up and restored with dental filling in order to maintain a crown restoration.

Merits of proposed circuits both in IC design and image processing make these circuits suitable choice for bioelectronics chips.

J10. A low-power pseudo-dynamic full adder cell for image addition.

Ayoub Sadeghi, Dr. Nabiollah Shiri, Mahmood Rafiee, Parisa Rahimi.

Computers & Electrical Engineering, Volume 87, 2020, https://doi.org/10.1016/j.compeleceng.2020.106787.

Integrated circuits (ICs) employ static and dynamic logic to improve performance and scalability.

This paper presents a new circuit design approach named pseudo-dynamic logic (PDL), which shows the advantages of both static and dynamic cells.

The PDL is evaluated by using a new full adder cell with 18 transistors.

In the presented full adder, gate diffusion input (GDI), transmission gate (TG), and float techniques are combined, and pull-up or pull-down networks are changed into a new configuration so that the number of transistors and internal nodes will decrease.

Post-layout simulations and digital image addition are performed to evaluate the real environment and practical application of the cell. Peak signal to noise ratio (PSNR), mean square error (MSE), and structural similarity index metric (SSIM) are calculated to study the cell performance in image processing. Compared to the dynamic and static circuits, the proposed PDL-based full adder cell performs better, and the results validate its effectiveness.